基于FPGA的多路脈沖重復(fù)頻率跟蹤器

在JTAG器件鏈中,兩個(gè)EPC2是第一和第二個(gè)器件,FPGA是第三個(gè)器件,JTAG按順序?qū)ζ骷幊坍?dāng)對(duì)FPGA編程時(shí),通過(guò)軟件將兩個(gè)EPC2設(shè)置成BYPASS模式,編程數(shù)據(jù)從EPC2的TDI管腳直接輸出到TDO管腳直達(dá)FPGA芯片,實(shí)現(xiàn)了對(duì)FPGA芯片的在線編程采用這種JTAG器件鏈方式,方便了系統(tǒng)調(diào)試,縮短了產(chǎn)品的開(kāi)發(fā)周期

3 FPGA應(yīng)用系統(tǒng)設(shè)計(jì)中應(yīng)注意的問(wèn)題

為了提高FPGA應(yīng)用系統(tǒng)的抗干擾性能,應(yīng)盡量采用多層印刷電路板,并有完整的GND層和電源層,從而提供幾乎無(wú)限的電流吸收能力,起到防止噪聲和為邏輯信號(hào)提供屏蔽的作用由于APEX EP20KE系列FPGA采用雙電壓體系,最好采用兩個(gè)電源層,一個(gè)作為核心電源層,一個(gè)作為I/O電源層本設(shè)計(jì)采用了八層電路板工藝,其中有兩個(gè)GND層一個(gè)核心電壓層一個(gè)I/O電壓層以及四個(gè)信號(hào)層,在實(shí)際調(diào)試中抗干擾性能明顯強(qiáng)于以前的雙面板系統(tǒng)如果在實(shí)際應(yīng)用中對(duì)價(jià)格敏感,也可采用四層板工藝,其中應(yīng)有一個(gè)完整的GND層,一個(gè)分割的電源層

FPGA器件的每一個(gè)電源和GND引腳都應(yīng)當(dāng)直接連接到電源和GND平面上,每一對(duì)電源和GND引腳都應(yīng)當(dāng)接上一個(gè)電源去耦電容器,而且盡可能靠近FPGA器件對(duì)于PQFP封裝的器件,應(yīng)當(dāng)把去耦電容器集中在器件正下方電路板焊接面上,這樣既達(dá)到了靠近器件的目的,又可以減少電路板的面積

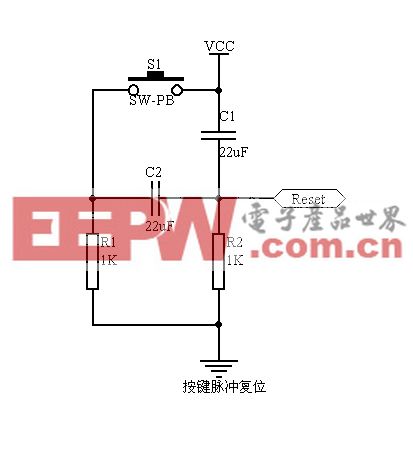

在電源線進(jìn)入電路板的地方一般都放置一個(gè)100μF的大容量電容器,以穩(wěn)定電源電壓,但是這個(gè)電容器有時(shí)也會(huì)成為導(dǎo)致FPGA器件配置失敗的隱患Altera器件在上電初始化時(shí),首先實(shí)行一個(gè)POR(上電復(fù)位)延遲以等待電源穩(wěn)定如果電源電壓上升時(shí)間較長(zhǎng),超過(guò)了POR延遲時(shí)間,可能造成器件初始化不正確,導(dǎo)致功能失效當(dāng)用EPC2配置APEX EP20KE系列FPGA時(shí),POR延遲最大為200ms,所以電源電壓上升時(shí)間不能超過(guò)這個(gè)時(shí)間如果出現(xiàn)系統(tǒng)上電時(shí)FPGA器件配置失敗的情況,應(yīng)當(dāng)考慮是否由于大容量電容器致使電源電壓上升太慢,這時(shí)可以更換一個(gè)小容量的電容器尤其是在單塊電路板上調(diào)試成功,而多塊電路板連在一起調(diào)試時(shí)出現(xiàn)這種情況更應(yīng)考慮這個(gè)原因因?yàn)槎鄩K電路板連在一起時(shí)電源濾波電容是并聯(lián)的,此時(shí)容量相加導(dǎo)致更大容量的電容出現(xiàn)在電源入口處,致使電壓上升過(guò)慢本系統(tǒng)在調(diào)試時(shí)就曾遇見(jiàn)這種情況,將電源濾波電容從100μF調(diào)整為22μF便解決了問(wèn)題

為了提高電路設(shè)計(jì)效率,應(yīng)盡量多采用LPM宏單元庫(kù)LPM是參數(shù)化的模塊庫(kù),是優(yōu)秀的版圖設(shè)計(jì)人員和軟件人員智慧的結(jié)晶LPM包括了常用的邏輯單元,通過(guò)修改LPM的某些參數(shù),就能迅速設(shè)計(jì)出自己的電路Altera公司提供的LPM宏單元庫(kù)是Altera系列FPGA器件的絕佳組合,可以實(shí)現(xiàn)絕大部分的設(shè)計(jì)功能,并能提供較高的運(yùn)行速度和較低的資源占用率在設(shè)計(jì)中發(fā)現(xiàn),多采用LPM宏單元庫(kù)的電路與不采用LPM宏單元庫(kù)的電路相比,資源占用率可減少10%~30%,可見(jiàn)節(jié)省的芯片資源是很可觀的

本設(shè)計(jì)利用FPGA設(shè)計(jì)靈活易于編程和容量大的特點(diǎn)實(shí)現(xiàn)了多路脈沖重復(fù)頻率跟蹤器,解決了在密集信號(hào)環(huán)境下跟蹤系統(tǒng)的實(shí)時(shí)性問(wèn)題,將八路跟蹤器設(shè)計(jì)在一片Altera公司的APEX EP20K200EQI FPGA芯片中,縮小了電路體積,滿足了系統(tǒng)小型化的要求實(shí)驗(yàn)證明用高性能FPGA實(shí)現(xiàn)多路脈沖跟蹤系統(tǒng)是完全可行的

濾波器相關(guān)文章:濾波器原理

fpga相關(guān)文章:fpga是什么

濾波器相關(guān)文章:濾波器原理

合成孔徑雷達(dá)相關(guān)文章:合成孔徑雷達(dá)原理 脈沖點(diǎn)火器相關(guān)文章:脈沖點(diǎn)火器原理

評(píng)論