3 參數(shù)設置

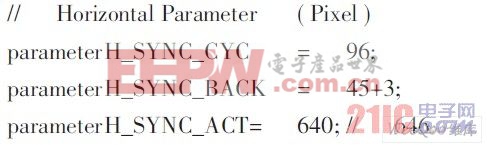

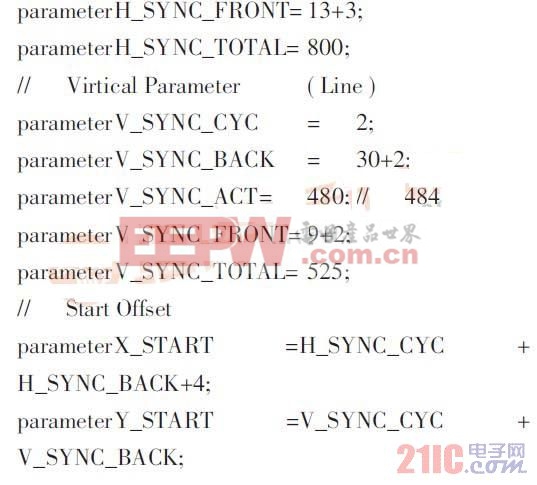

本系統(tǒng)采用640×480 像素顯示, 刷新率為60Hz模式���, 像素時鐘為25MHz����。在VGA水平時序中��, 每行包括800像素點�, 其中640為有效顯示脈沖, 160為行消隱區(qū)����; 而在VGA垂直時序中����, 每場525行, 其中480有效����, 45行為場消隱。其具體參數(shù)如下:

4 結(jié)束語

本文介紹的圖像采集和顯示模塊設計簡單,成本較低��。由于其用高效硬件描述語言構(gòu)成�, 故其處理效率高, 具有很好的實用特性���。

評論