基于Spartan-6 FPGA的SP605開發(fā)板解決文案

Surveillance Image Capture and Analytics Engine Integrate sensor interfacing, video analytics, image enhancement and network interfacing in a single Spartan-6 LX150T FPGA.

圖3.監(jiān)視圖像捕捉和分析引擎系統(tǒng)

Spartan®-6 FPGA SP605評估板

The Spartan®-6 FPGA SP605 Evaluation Kit conveniently delivers all the basic components for developing broadcast, wireless communications, automotive, and other cost- and power-sensitive applications that require transceiver capabilities in one ackage. Along with the evaluation board, cables, and documentation, the SP605 Evaluation Kit provides an integration of hardware, software, intellectual property (IP), and pre-verified reference designs so development can begin right out of the box.

The SP605 Evaluation Kit provides a flexible environment for higher-level system design, including applications that implement features such as high-speed serial transceivers, PCI Express®, DVI, and/or DDR3. The SP605 evaluation board includes an industry-standard FPGA Mezzanine Card (FMC) connector for scaling and customizing to specific applications and markets. The integration of Xilinx development tools help streamline the creation of systems that adhere to complex requirements.

This guide provides steps to setup the SP605 hardware and run a diagnostic demonstration that exercises a number of basic board features. It introduces a more complex Base Reference Design that exercises key features of the Spartan-6 FPGA. This guide also provides steps for installing the Xilinx® ISE® Design Suite: Logic Edition software, obtaining updates, and generating a license.

SP605評估板包括:

Spartan-6 FPGA SP605 Evaluation Board

ISE Design Suite Logic Edition: (device-locked) for Spartan-6 LX45T FPGA

Includes ChipScope Pro software and the ChipScope Pro Serial I/O Toolkit

Includes PlanAhead Design Analysis Tool

Timing Driven Place and Route, SmartGuide, and SmartXplorer Technology

Documentation

Hardware Setup Guide

Getting Started Guide

Hardware User Guide

Reference Design User Guide

Schematics and PCB files

Universal 12V power supply

Cables

(2) USB

Ethernet

DVI to VGA adapter

Reference Designs and Demonstrations

Board Diagnostic Demonstration

Base Reference Design featuring DSP48, Ethernet, memory, and serial transceiver integration

MultiBoot Reference Design, featuring fail-safe configuration

Integrated Memory Controller Reference Design

Integrated Bit Error Ratio (IBERT) Reference Design

PCIe® x1 Gen1 Reference Design

Reference designs, demonstrations, documentation, and applications delivered on USB Flash drive to get started quickly

SP605評估板主要特性:

Spartan-6 FPGA

XC6SLX45T-3FGG484 device

Configuration

Onboard JTAG configuration circuitry

8 MB Quad SPI Flash

32 MB Parallel (BPI) Flash

System ACE CF 2 GB CompactFlash (CF) card Memory

128 MB DDR3 Component Memory

32 MB Parallel (BPI) Flash (Also available for configuration)

8 Kb IIC EEPROM

128 MB Quad SPI Flash (Also available for configuration) Communications and Networking

10/100/1000 Tri-Speed Ethernet

SFP transceiver connector

GTP port (TX, RX) with four SMA connectors

USB To UART bridge

PCI Express x1 edge connector Expansion Connectors

FMC LPC connector (1 GTP transceiver, 68 single-ended or 34 differential userdefined

signals)

User GPIO with two SMA connectors

4 user I/O (1 x 6 header) Clocking

200 MHz oscillator (differential)

27 MHz Socketed oscillator (single-ended)

SMA connectors for external clock (differential)

GTP reference clock port with two SMA connectors Display

Video - DVI / VGA

16 x 2 LCD character display

4 LEDs Control

4 Pushbuttons

4 DIP switches Power

12V wall adapter or ATX

Voltage and current measurement capability of 2.5V, 1.5V, and 1.2V supplies

圖4.Spartan®-6 FPGA SP605評估板外形圖

圖5.Spartan®-6 FPGA SP605評估板方框圖和外設(shè)

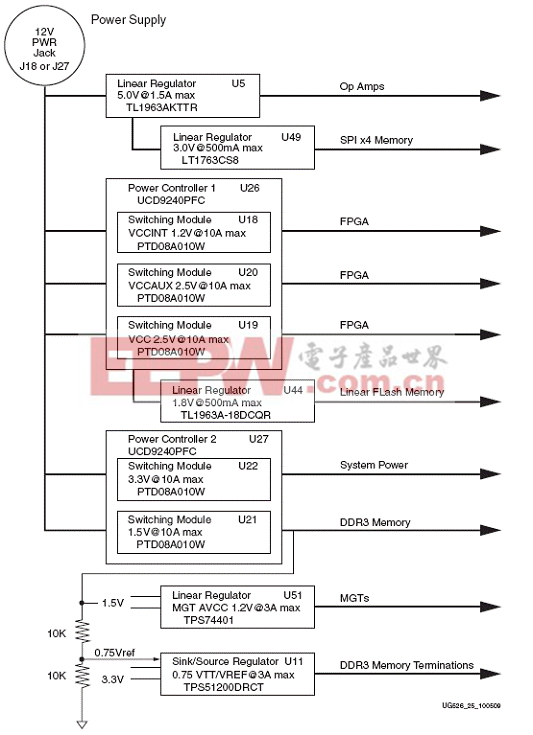

圖6. SP605評估板板載電源穩(wěn)壓器框圖

評論