雙核DSP片TMS320VC5421并行引導(dǎo)方案

1引言

本文引用地址:http://2s4d.com/article/257224.htm TMS320VC54211、2(以下簡稱VC5421)是TI公司推出的一款雙核定點(diǎn)DSP芯片,它擁有兩個(gè)DSP子系統(tǒng),每個(gè)子系統(tǒng)都有一個(gè)DSP核,并且均有獨(dú)立的數(shù)據(jù)和程序存儲空間,可以進(jìn)行兩核之間的通信,并且兩個(gè)子系統(tǒng)共享一套片外總線。

此外,每個(gè)子系統(tǒng)各自擁有2k 16bit字的片內(nèi)ROM,并存儲有Bootloader程序。當(dāng)DSP芯片上電或復(fù)位時(shí),兩個(gè)DSP核可分別啟動自身獨(dú)立的Bootloader程序,以實(shí)現(xiàn)用戶程序的上電自舉。

雙核DSP自啟動和單核DSP自啟動的實(shí)現(xiàn)方法有較大的差別,這一點(diǎn)在DSP系統(tǒng)設(shè)計(jì)中需要特別注意。本文對雙核DSP芯片VC5421的引導(dǎo)模式進(jìn)行了深入的分析和研究,給出了使用16位并行引導(dǎo)模式進(jìn)行雙核DSP引導(dǎo)的實(shí)現(xiàn)方案。

2 TMS320VC5421的Boot模式

其中16位并行引導(dǎo)模式是通過片外存儲器接口(EMIF)以DMA方式將代碼從16-bit字寬的片外數(shù)據(jù)存儲器搬移到片內(nèi)程序存儲空間;

8位并行引導(dǎo)模式則是通過片外存儲器接口(EMIF)以DMA方式將代碼從8-bit字寬的片外數(shù)據(jù)存儲器搬移到片內(nèi)的程序存儲空間;

而串行EEPROM引導(dǎo)模式主要是通過多通道緩沖串口2(McBSP 2)從主設(shè)備中搬移代碼并實(shí)現(xiàn)上電自舉。

和54系列中其它芯片不同的是,VC5421片內(nèi)ROM中的Bootloader程序并不支持HPI、并行I/O和標(biāo)準(zhǔn)串口模式的自啟動方式。在其所支持的三種boot模式中,16位并行引導(dǎo)模式是最常用的。本文對這種模式進(jìn)行了深入分析,給出了使用該模式進(jìn)行雙核DSP程序引導(dǎo)的方案,并通過實(shí)驗(yàn)驗(yàn)證了該方案的正確性。

2.1 并行引導(dǎo)模式的選擇

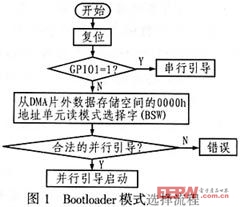

?。郑茫担矗玻钡膬蓚€(gè)DSP核在DSP芯片上電或復(fù)位時(shí),到底以哪種模式實(shí)現(xiàn)上電自舉,主要由兩個(gè)核的公共引腳XIO和各自的GPIO0/ROMEN、GPIO1引腳決定。當(dāng)XIO為0(低電平)時(shí),將不從ROM引導(dǎo),也就是說,將不使用VC5421片內(nèi)ROM中的Bootloader程序?qū)崿F(xiàn)上電引導(dǎo),而是用HPI模式實(shí)現(xiàn)上電自舉;當(dāng)XIO為1(高電平),GPIO0/ROMEN為0時(shí),將使用片外存儲器中用戶自己編寫的Bootloader程序?qū)崿F(xiàn)上電自舉;當(dāng)XIO為1 GPIO/ROMEN為1 GPIO1為0或1時(shí),將分別使用并行或者串行引導(dǎo)模式實(shí)現(xiàn)上電自舉。因此,在實(shí)施相應(yīng)的上電自舉前,必須將引腳狀態(tài)設(shè)置正確,以保證Bootloader程序按預(yù)定的模式執(zhí)行。Bootloader模式的選擇流程見圖1。

當(dāng)Bootloader程序檢測到并行引導(dǎo)模式時(shí),程序?qū)⒁裕模停练绞綇钠鈹?shù)據(jù)存儲區(qū)的0000h單元取出模式選擇字(BSW)來進(jìn)一步?jīng)Q定是8位還是16位的并行引導(dǎo)模式。10AAh意味著選擇了16位并行引導(dǎo)模式,而如果選擇8位并行引導(dǎo)模式,取出的兩個(gè)字節(jié)將是08h和AAh。之后,程序?qū)凑眨拢铮铮舯磉M(jìn)行加載。圖2是并行引導(dǎo)模式的選擇流程。

2.2 16位并行引導(dǎo)模式的Boot表

?。拢铮铮簦欤铮幔洌澹虺绦蛞嵋频拇a必須組織成一定的格式,這就是Boot表。16位并行引導(dǎo)模式的Boot表如表1所列。

表1 16位并行導(dǎo)模式Boot表

此外,需要注意的是,由于在多數(shù)程序中都有跳轉(zhuǎn)指令或循環(huán)指令,所以,Boot表中的程序入口地址必須和程序的cmd文件中分配的地址保持一致,也就是說,當(dāng)在CCS中進(jìn)行調(diào)試時(shí),如果程序Load到5000h,Boot表中的程序入口地址就應(yīng)該是5000h。

2.3 Boot表的生成

Boot表可由hex500格式轉(zhuǎn)換工具生成,也可以自己編寫一個(gè)文件格式轉(zhuǎn)換程序來把.out文件轉(zhuǎn)換成所需的文件格式。本設(shè)計(jì)通過編寫一個(gè)C++程序來將.out文件轉(zhuǎn)換成.hex文件,然后再在文件的開始處增加相應(yīng)的標(biāo)志位和寄存器設(shè)置字,從而形成完整的Boot表。

?。?VC5421片外總線沖突的解決方案

由于VC5421是雙核DSP,每個(gè)核有各自的存儲空間和Bootloader程序,但兩核共享一套片外總線和一個(gè)XIO引腳。這樣,當(dāng)兩核的復(fù)位引腳A_RS和B_RS同時(shí)收到復(fù)位低電平信號時(shí),將同時(shí)申請片外總線的控制權(quán)。這就造成了申請片外總線的沖突。而且Bootloader程序總是檢查該核有沒有片外總線的控制權(quán),如果沒有,將循環(huán)檢查直到取得片外總線的控制權(quán)。為了避免這種情況的發(fā)生,應(yīng)該以合理的順序給兩個(gè)核上電。

由于VC5421中A核帶有用來控制時(shí)鐘頻率的鎖相環(huán)電路,所以應(yīng)該先對A核進(jìn)行復(fù)位,再啟動A核,然后利用A核的用戶程序來控制B核的復(fù)位,以實(shí)現(xiàn)兩個(gè)核的啟動。

根據(jù)系統(tǒng)需要,本設(shè)計(jì)使用Altera公司的CPLD芯片來產(chǎn)生各種控制信號。其電路連接示意圖如圖3所示。A核的復(fù)位信號A_RS由CPLD芯片直接給出,并在系統(tǒng)上電或復(fù)位的同時(shí)對A核進(jìn)行復(fù)位。而B核的復(fù)位信號B_RS則通過CPLD映射到DSP的I/O空間0000h地址單元的第6位:B核復(fù)位控制位(在系統(tǒng)復(fù)位后值為0)如圖4所示。在A核啟動后,通過用戶程序?qū)懀拢撸遥游豢蔀椋潞颂峁?fù)位信號。

?。?VC5421的并行引導(dǎo)自啟動操作

4.1 用戶程序的搬移

兩個(gè)DSP核要完成各自的功能,執(zhí)行的用戶程序是不盡相同的,而且A核的用戶程序還要控制B核的復(fù)位,因此兩個(gè)DSP核的Boot表內(nèi)容是不同的。由DMA方式內(nèi)部存儲器圖可知,程序空間的第0頁和第1頁屬于A核,第2頁和第3頁屬于B核。因此,需要注意的是,當(dāng)Bootloader程序搬移用戶程序時(shí),A核的用戶程序要被搬移到內(nèi)部程序空間的第0頁上,而B核的用戶程序則要被搬移到第2頁上。于是B核Boot表中的程序入口XPC和目的XPC應(yīng)被設(shè)置成0002h。

?。矗?Boot表的放置

本系統(tǒng)用4Mbit(256k×16)FLASH器件SST39VF400A作為片外數(shù)據(jù)存儲器。頁選信號由DSP通過CPLD給出,并且映射到DSP中I/O空間的0000h地址單元的低5位(系統(tǒng)復(fù)位后5位均為0,即第0頁)。如圖4所示。另外,此地址單元的第5位(CFG位)是控制FLASH映射的配置位。當(dāng)CFG為0時(shí),FLASH被映射到DMA片外數(shù)據(jù)空間的0000h,此時(shí),Bootloader程序可以以DMA方式從FLASH中搬移數(shù)據(jù)并進(jìn)行自啟動;當(dāng)CFG為1時(shí),FLASH被映射到CPU片外數(shù)據(jù)空間的8000h,在這種情況下,可以通過程序向FLASH中燒寫數(shù)據(jù)。因此,這一位在系統(tǒng)上電或復(fù)位后將被設(shè)置成0,以使A核能夠順利啟動。

由于兩個(gè)DSP核的Boot表內(nèi)容不同,故應(yīng)視Boot表的大小,將兩個(gè)Boot表放到FLASH的不同頁上,以便對兩個(gè)核分別實(shí)行引導(dǎo)。本設(shè)計(jì)將A核的Boot表放到第0頁,將B核的Boot表放到第1頁。

?。矗?外總線控制權(quán)的釋放

如圖5所示,在GPIO控制寄存器(地址3Ch)中,XIO_GRANT位為1代表相應(yīng)的DSP核取得了片外總線的控制權(quán);而在還沒有取得控制權(quán)(XIO_GRANT位為0)但在申請片外總線的控制權(quán)時(shí),相應(yīng)的XIO_REQ位應(yīng)置為1;CORE_SEL位用于表示程序在哪個(gè)核上運(yùn)行,當(dāng)在CPU A上運(yùn)行時(shí),讀A核的GPIO控制寄存器的CORE_SEL位將返回到“0”,而當(dāng)同一個(gè)程序在CPU B上運(yùn)行時(shí),讀B核的GPIO控制寄存器的CORE_SEL位將返回到“1”。有關(guān)GPIO控制寄存器的其它相關(guān)位,設(shè)計(jì)時(shí)可查閱有關(guān)的參考文獻(xiàn)1。

4.4 FLASH的燒寫

筆者根據(jù)SST39VF400A的資料編寫了一個(gè)DSP程序,該程序可同時(shí)將A核的Boot表燒寫到FLASH的第0頁,而將B核的Boot表燒寫到第1頁。

在系統(tǒng)上電或復(fù)位后,A核首先運(yùn)行它的Boot-loader程序(此時(shí)FLASH的第0頁映射到DMA片外數(shù)據(jù)空間的0000h地址單元),A核啟動后執(zhí)行用戶程序。用戶程序首先將頁選設(shè)置成第1頁,這樣,FLASH的第一頁將被映射到DMA片外數(shù)據(jù)空間的0000h;然后,A核釋放片外總線控制權(quán),并給B核發(fā)出復(fù)位信號,此時(shí)由于只有B核復(fù)位,且A核已釋放片外總線的控制權(quán),因此,B核將申請到片外總線控制權(quán),同時(shí)執(zhí)行Bootloader程序的啟動以完成整個(gè)DSP引導(dǎo)。完整的啟動過程流程圖如圖6所示,下面是A核的啟動測試程序代碼:

*mmregs

*titlc ″testLEDA″

*global begin

*text

.............

begin stm #0x000,0x0061 ;設(shè)置頁選信號

portw ox0061,00h

call wait

andm #0xffcf,3ch ;釋放片外總線

call wait ; 控制權(quán)

stm #0x00410x0061 ;給B核復(fù)位信號

portw 0x0061,00hcall wait

stm #0x0001,0x0061

portw 0x0061,00h

flash: rsbs 1,xf ;發(fā)光二極管亮

call wait

ssbx 1,xf ;發(fā)光二極管滅

call wait

b flash

;----Subroutine to wait for some time----

wait: stm #80,ar6

loop0: stm #30000,ar7-

loop1: nop

banz loop1,*ar7-

banz loop0,*ar6-

ret

?。?實(shí)驗(yàn)驗(yàn)證

本設(shè)計(jì)中,在DSP的A_XF和B_XF腳上連接兩個(gè)發(fā)光二極管,同時(shí)使被加載的用戶程序通過循環(huán)來設(shè)置/清除這兩個(gè)引腳以使兩個(gè)發(fā)光二極管以不同的頻率閃爍,以此來驗(yàn)證用戶程序是否成功加載。系統(tǒng)上電后,兩個(gè)發(fā)光二極管先后以不同的頻率開始閃爍,說明DSP的A核、B核均成功地實(shí)現(xiàn)了上電自舉。

c++相關(guān)文章:c++教程

評論