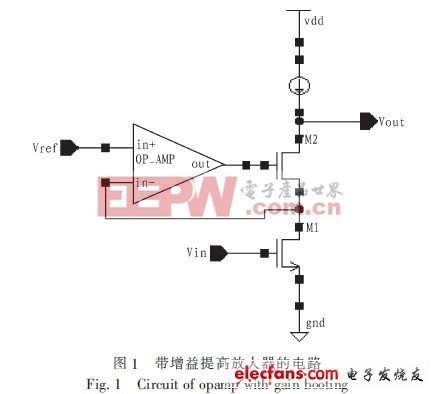

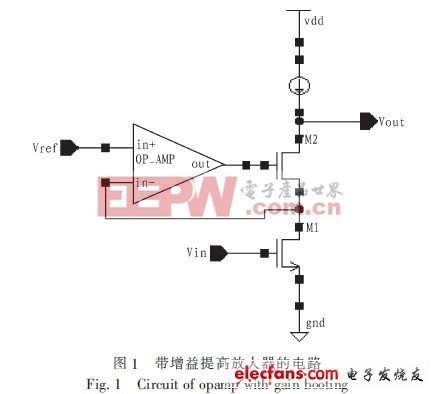

設(shè)計(jì)了一種用于高速ADC中的高速高增益的全差分CMOS運(yùn)算放大器�����。主運(yùn)放采用帶開(kāi)關(guān)電容共模反饋的折疊式共源共柵結(jié)構(gòu)���,利用增益提高和三支路電流基準(zhǔn)技術(shù)實(shí)現(xiàn)一個(gè)可用于12~14 bit精度,100 MS/s采樣頻率的高速流水線(Pipelined)ADC的運(yùn)放��。設(shè)計(jì)基于SMIC 0.25 μm CMOS工藝,在Cadence環(huán)境下對(duì)電路進(jìn)行Spectre仿真�����。仿真結(jié)果表明��,在2.5 V單電源電壓下驅(qū)動(dòng)2 pF負(fù)載時(shí)����,運(yùn)放的直流增益可達(dá)到124 dB,單位增益帶寬720 MHz�����,轉(zhuǎn)換速率高達(dá)885 V/μs�,達(dá)到0.1%的穩(wěn)定精度的建立時(shí)間只需4 ns,共模抑制比153 dB����。

評(píng)論