STM32 APB1總線時鐘配置問題

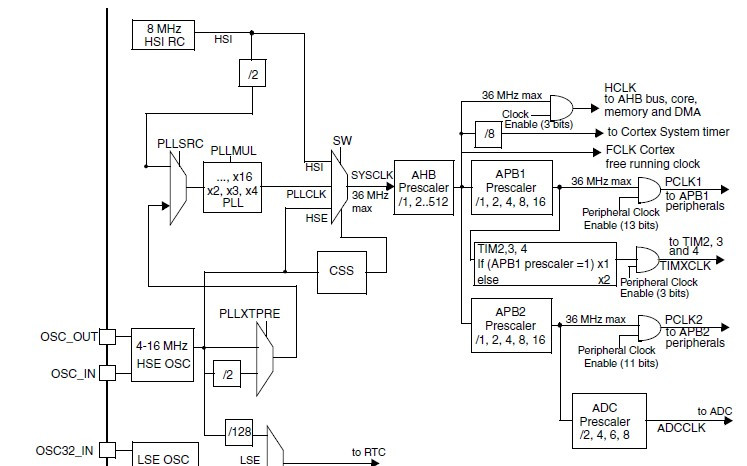

圖2 STM32 時鐘系統(tǒng)

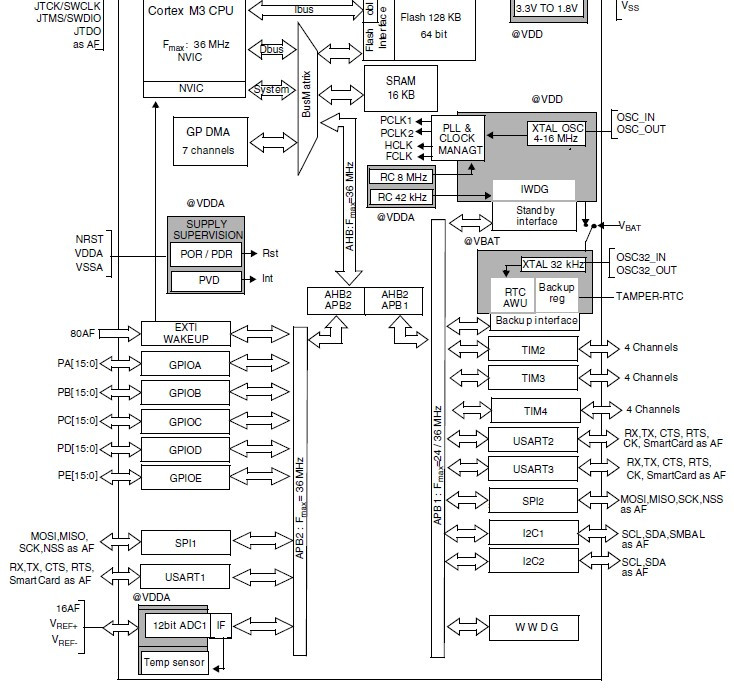

從圖1可以看到APB1總線掛接了TIM2~4,UART2~2...WWD等設(shè)備。然后從圖2中可以看到只有外設(shè)直接使用了APB1的時鐘作為實際時鐘,而TIM2~4根據(jù)APB1的時鐘進行了調(diào)整。因此當(dāng)設(shè)備B的PCLK1配置為1/2HCLK時實際上就是將APB1配置為了1/2HCLK,此時因為APB1的分頻系數(shù)不為1,因此TIM2~4使用的時鐘自動2倍頻,實際頻率就是HCLK了。由于先2分頻再2倍頻理論上是和HCLK一致,但電路結(jié)構(gòu)等因素將導(dǎo)致得到的結(jié)果和直接賦予HCLK不完全一致,導(dǎo)致通訊不穩(wěn)定。最終通過調(diào)整A設(shè)備的PCLK1也為1/2HCLK,可以穩(wěn)定通信。

評論