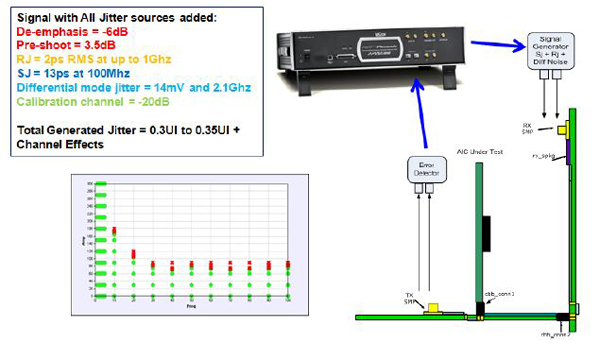

PCIE 3.0接收端抖動容限測試設(shè)置及連接示意圖及測試結(jié)果:

2012-12-18 11:26:35 上傳

下載附件 (139.15 KB)

接收機測試推薦使用的碼型為Modified Compliance Pattern�;對于Add-In Card被測件來說,誤碼測試儀輸出的100MHz的時鐘需要連接到CBB板的時鐘輸入端口�;對于System被測件來說,CLB板上來自于被測系統(tǒng)的100MHz時鐘輸出需要連接到誤碼儀的參考時鐘輸入�,經(jīng)過規(guī)范要求的PLL濾波后,用于驅(qū)動儀器的信號傳輸�。誤碼儀做誤碼檢測時需要過濾到為了信號同步而插入的SKP碼。

評論